Autor: Mauro Benito Montoya Arenas (mauro2017pre@gmail.com)

Laboratorio N°3: Logica transistores de paso – lógica CMOS estática

INTRODUCCION:

La

mayor utilidad del software Microwind es la posibilidad que le brinda al

usuario de “meterse” dentro de un circuito integrado (CI) a construir,

ampliando así las posibilidades de diseño del mismo y sus características

mínimas para que cumpla con determinados comportamientos requeridos. Una vez

que se adquiere un conocimiento adecuado de este paquete es posible construir

elementos y configuraciones de manera personalizada y a la vez cumpliendo con

requisitos mínimos de diseño dependiendo de la tecnología a trabajar.

OBJETIVOS:

Ø Hacer los layouts del flip-flop tipo D y JK del ejercicio A, y construir el layout del ejercicio B.

Ø Aprender el funcionamiento de los layouts implementados en el ejercicio A y B.

Ø Detallar

las características y comportamientos dinámicos de los circuitos

TEMA PROPUESTO:

Laboratorio

Nº3

BASES TEORICAS:

a)

Marco

Teórico:

Tecnología CMOS:

CMOS o MOSFET complementaria tiene una gran aplicación en el diseño de lógica de computadora. La relativamente alta impedancia de entrada, las rapidas velocidades de conmutación y los bajos niveles de potencia de operación de la configuración CMOS, han dado por resultado una disciplina totalmente nueva conocida como diseño de lógica CMOS [1].

Figura 1. CMOS inversor

Figura 2. Símbolos de los nMOS y pMOS

Figura 3. Característica del MOSFET de enriquecimiento que muestra las condiciones de encendido y apagado: (a) nMOS; (b) pMOS

b) Marco conceptual:

Software Microwind:Descripción: Microwind es una herramienta para diseñar y simular circuitos a nivel de diseño. La herramienta cuenta con funciones de edición completas (copiar, cortar, pegar, duplicar, mover), varias vistas (MOS características, sección transversal 2D, visor de procesos 3D), y un simulador analógico. Resulta engorroso, que siendo la primera vez que una persona trabaje en un software, se encuentre con una cantidad de términos desconocidos y no muy fáciles de entender. Microwind es uno de los paquetes donde más acontece esta dificultad, por tanto, es útil conocer algunos conceptos básicos del programa [2]: - Reglas de diseño: Para Microwind, son una compilación de reglas geométricas, de propiedades eléctricas, químicas, y de parámetros de modelo, que juntas conforman una tecnología de proceso de construcción de circuitos integrados (CI’s).- Archivos RUL: Bajo esta extensión se guardan los archivos que contienen las reglas de diseño para Microwind.- Tecnología de proceso: Consiste en un conjunto de reglas de diseño, que permiten construircircuitos integrados con determinadas caracteristicas.- Layout: Disposición de capas, o layers, que representan la litografía de dispositivos en un circuito integrado. En palabras más castizas, es un conjunto de máscaras, las cuales representan materiales, que son constitutivos de dispositivos a implementarse en un CI.Figura 4. Layout de un sumador medio hecho en Microwind

- Layer: Disposición de capas o mascaras que forman un Layout. Layers diferentes representan diferentes tipos de material, los cuales tienen usos específicos dentro de un layout.

- Workspace o “fondo negro”: Como su nombre indica, es el fondo negro en el cual se construyen los layouts de Microwind. Representa en realidad una gran oblea lineal, isotrópica y homogénea de silicio dopado de tipo P, de dimensiones infinitas.

- Lambda (𝝀): Es una escala de longitud que utiliza Microwind, para ajustar distancias a la tecnología empleada. No debe confundirse este lambda, con el lambda (𝜆) del modelo del modelo de segundo orden del transistor MOSFET operando en región de saturación. Para la tecnología, el valor lambda es ajustado a la mitad del largo del canal de un transistor MOS, por defecto.

Figura 5. Valor de lambda por defecto en Microwind- Lambda grid: Es una cuadricula dispuesta sobre el workspace del microwind, escalada en lambdas, que sirve como referencia para ajustar distancias en la construcción de un layout.

DESARROLLO DEL TRABAJO:

A) Para circuito mostrado:

1) Analizar y determinar la función lógica de salida del circuito. Presentar completo el LAYOUT (manual con transistores de dimensiones mínimas) y corroborar su función lógica mediante simulación. Medir el ÁREA del layout y hallar la frecuencia MÁXIMA de operación (Revisar el método para determinar la frecuencia de operación máxima de un circuito secuencial)

Figura . Circuito del

ejercicio A

En primer lugar, analizamos la tabla de la verdad del circuito:

|

D |

CLK |

Q |

|

|

0 |

0 |

NC |

NC |

|

0 |

1 |

0 |

1 |

|

1 |

0 |

NC |

NC |

|

1 |

1 |

1 |

0 |

Con la tabla de la verdad ya realizada. Hacemos ahora el mapa de Karnaugh:

|

D |

|

|

|

|

0 |

1 |

|

|

|

X |

X |

0 |

CLK |

|

0 |

|

1 |

|

Del mapa de Karnaugh podemos hallar finalmente, las ecuaciones de F: F=D

Pasamos ahora a crear el layout correspondiente al circuito:

Figura . Layout del

circuito del ejercicio A parte 1

Comprobamos la ecuación encontrada con el comportamiento dinámico del layout, que debe ser igual que el análisis teórico:

Figura . Comportamiento dinámico

del ejercicio A parte 1

El comportamiento dinámico del circuito demuestra que las ecuaciones halladas teóricamente son correctas.

Área del layout

Figura . Medición del área del layout

Podemos darnos cuenta que el layout tiene un ancho de 110𝜆 y de largo 58𝜆, por lo que el layout tendrá un área total de: 6380𝜆^2=99.6875um^2 .

Frecuencia

máxima de operación

El nuevo comportamiento dinámico del layout será como se muestra en la figura. Podemos observar que no se marca ningún retraso:

Figura . Nuevo comportamiento del circuito con fsimulacion=10MHz

2) En base al layout de la parte 1, implementar un FF tipo J-K disparado por flanco de subida. Hacer el layout manual de dimensiones mínimas y corroborar su función lógica mediante simulación. Medir el ÁREA del layout y hallar la frecuencia MÁXIMA de operación. (Revisar el método para determinar la frecuencia de operación máxima de un circuito secuencial)

Como ya obtuvimos la tabla de la verdad del FF tipo D. Debemos hacer una igualdad con la tabla de la verdad del FF tipo JK.

|

J |

K |

Qt |

Qt+1 |

D |

|

0 |

X |

0 |

0 |

0 |

|

1 |

X |

0 |

1 |

1 |

|

X |

1 |

1 |

0 |

0 |

|

X |

0 |

1 |

1 |

1 |

Aplicando

Karnaugh, se obtiene la ecuación correspondiente al circuito de entrada del

biestable D:

|

AB |

|

|

|

|

|

|

00 |

01 |

11 |

10 |

|

|

|

1 |

1 |

1 |

|

00 |

Qt |

|

1 |

0 |

0 |

|

01 |

|

El circuito será el siguiente:

Figura . Flip Flop JK

apartir del flip flop D

B) Para circuito mostrado:

Analizar y

determinar la función lógica de salida del circuito y dibuje el circuito

esquemático de transistores. Presentar completo el LAYOUT (manual con

transistores de dimensiones mínimas) y corroborar su función lógica mediante

simulación. Medir el ÁREA del layout y hallar la frecuencia MÁXIMA de

operación.

Figura . Layout del

circuito

Para determinar la función lógica del circuito primero vamos a identificar cual es la configuración de transistores n-MOS:

Figura . Circuito

representado por transistores

Podemos realizar ahora la tabla de la verdad del circuito. Primero debemos observar que, cuando la salida no está a tierra (0), debe estar a fuente (1). Conocemos las veces en las que el circuito está a tierra (por la red pull-down), cuando el circuito no marca tierra completamos el resto con 1.

|

A |

B |

C |

D |

F |

|

|

0 |

0 |

0 |

0 |

1 |

A fuente |

|

0 |

0 |

0 |

1 |

1 |

A fuente |

|

0 |

0 |

1 |

0 |

1 |

A fuente |

|

0 |

0 |

1 |

1 |

1 |

A fuente |

|

0 |

1 |

0 |

0 |

1 |

A fuente |

|

0 |

1 |

0 |

1 |

0 |

A tierra |

|

0 |

1 |

1 |

0 |

0 |

A tierra |

|

0 |

1 |

1 |

1 |

0 |

A tierra |

|

1 |

0 |

0 |

0 |

1 |

A fuente |

|

1 |

0 |

0 |

1 |

0 |

A tierra |

|

1 |

0 |

1 |

0 |

0 |

A tierra |

|

1 |

0 |

1 |

1 |

0 |

A tierra |

|

1 |

1 |

0 |

0 |

1 |

A fuente |

|

1 |

1 |

0 |

1 |

0 |

A tierra |

|

1 |

1 |

1 |

0 |

0 |

A tierra |

|

1 |

1 |

1 |

1 |

0 |

A tierra |

Realizamos ahora el mapa de Karnaugh.

|

AB |

|

|

|

|

|

|

|

01 |

11 |

10 |

|

|

|

1 |

1 |

1 |

1 |

00 |

CD |

|

1 |

0 |

0 |

0 |

01 |

|

|

1 |

0 |

0 |

0 |

11 |

|

|

1 |

0 |

0 |

0 |

10 |

|

Por el mapa de Karnaugh nos podemos dar cuenta de que:

Figura . Se muestra el

circuito completo

Con

el esquema del circuito completo ya podemos armar el layout:

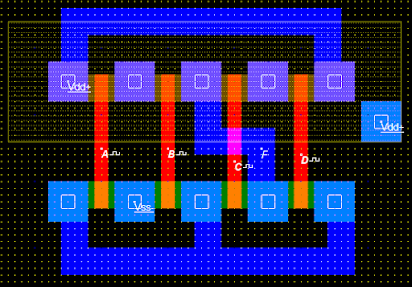

Figura . Layout del

circuito

Comportamiento dinámico del circuito

Figura . Comportamiento dinámico

del circuito

Observando

el comportamiento dinámico del circuito podemos ver que se cumple la tabla de

la verdad y el circuito funciona de manera correcta.

Área

del layout

Figura . Medimos el área

del layout

Con el botón de “Measure distance” medimos e ancho y largo en lambdas.

Frecuencia

máxima de operación

Vista 3D

Figura . Transistores en

el layout

Figura . Vista de corte 3D del Layout

CONCLUSIONES:

Ø El layout mínimo de un circuito sirve para ahorrar área y aumentar la frecuencia máxima de trabajo.

Ø Con la vista de corte 2D y la vista 3D podemos observar los componentes de los layouts creados.

Ø En el archivo *.cir se encuentra la información del layout creado. Datos técnicos tales como: las capacitancias parasitas, W, L, el tipo de modelo del transistor, etc.

Ø En

el archivo *.cif se encuentra la posición de los polígonos del polisilicio,

sustrato tipo p y n, difusión p y n, etc.