Autor: Mauro Benito Montoya Arenas (mauro2017pre@gmail.com)

LABORATORIO 1: LAYOUT DE TRANSISTORES MOS

RESUMEN:

En

este laboratorio hemos creado el layout de un transistror tipo N y otro tipo P

usando el software Microwind, además hemos obtenido sus características

(dinámicas y estáticas) y descripciones físicas. También hemos revisado el

funcionamiento de los transistores, hemos aprendido sobre la tecnología CMOS y

sobre el modelo teórico de spice shichman hodges.

INTRODUCCION:

La

mayor utilidad del software Microwind es la posibilidad que le brinda al

usuario de “meterse” dentro de un circuito integrado (CI) a construir,

ampliando así las posibilidades de diseño del mismo y sus características

mínimas para que cumpla con determinados comportamientos requeridos. Una vez

que se adquiere un conocimiento adecuado de este paquete es posible construir

elementos y configuraciones de manera personalizada y a la vez cumpliendo con

requisitos mínimos de diseño dependiendo de la tecnología a trabajar.

OBJETIVOS:

Ø Hacer las simulaciones del transistor N-MOS y P-MOS usando el software Microwind.

Ø Aprender el funcionamiento de un MOSFET.

Ø Detallar

las características de los transistores N-MOS y P-MOS

TEMA PROPUESTO:

Layout

de transistores MOS

BASES TEORICAS:

a)

Marco

Teórico:

Tecnología CMOS:

CMOS o MOSFET complementaria tiene una gran aplicación en el diseño de lógica de computadora. La relativamente alta impedancia de entrada, las rapidas velocidades de conmutación y los bajos niveles de potencia de operación de la configuración CMOS, han dado por resultado una disciplina totalmente nueva conocida como diseño de lógica CMOS [1].

Figura 1. CMOS inversor

Figura 2. Símbolos de los

nMOS y pMOS

Figura 3. Característica

del MOSFET de enriquecimiento que muestra las condiciones de encendido y

apagado: (a) nMOS; (b) pMOS

b)

Marco

conceptual:

Software Microwind:Descripción: Microwind es una herramienta para diseñar y simular circuitos a nivel de diseño. La herramienta cuenta con funciones de edición completas (copiar, cortar, pegar, duplicar, mover), varias vistas (MOS características, sección transversal 2D, visor de procesos 3D), y un simulador analógico. Resulta engorroso, que siendo la primera vez que una persona trabaje en un software, se encuentre con una cantidad de términos desconocidos y no muy fáciles de entender. Microwind es uno de los paquetes donde más acontece esta dificultad, por tanto, es útil conocer algunos conceptos básicos del programa [2]: - Reglas de diseño: Para Microwind, son una compilación de reglas geométricas, de propiedades eléctricas, químicas, y de parámetros de modelo, que juntas conforman una tecnología de proceso de construcción de circuitos integrados (CI’s).- Archivos RUL: Bajo esta extensión se guardan los archivos que contienen las reglas de diseño para Microwind.- Tecnología de proceso: Consiste en un conjunto de reglas de diseño, que permiten construircircuitos integrados con determinadas caracteristicas.- Layout: Disposición de capas, o layers, que representan la litografía de dispositivos en un circuito integrado. En palabras más castizas, es un conjunto de máscaras, las cuales representan materiales, que son constitutivos de dispositivos a implementarse en un CI.Figura 4. Layout de un sumador medio hecho en Microwind

- Layer: Disposición de capas o mascaras que forman un Layout. Layers diferentes representan diferentes tipos de material, los cuales tienen usos específicos dentro de un layout.

- Workspace o “fondo negro”: Como su nombre indica, es el fondo negro en el cual se construyen los layouts de Microwind. Representa en realidad una gran oblea lineal, isotrópica y homogénea de silicio dopado de tipo P, de dimensiones infinitas.

- Lambda (𝝀): Es una escala de longitud que utiliza Microwind, para ajustar distancias a la tecnología empleada. No debe confundirse este lambda, con el lambda (𝜆) del modelo del modelo de segundo orden del transistor MOSFET operando en región de saturación. Para la tecnología, el valor lambda es ajustado a la mitad del largo del canal de un transistor MOS, por defecto.

Figura 5. Valor de lambda por defecto en Microwind

- Lambda grid: Es una cuadricula dispuesta sobre el workspace del microwind, escalada en lambdas, que sirve como referencia para ajustar distancias en la construcción de un layout.

Botones (funciones) de Microwind [3]:Figura 6. Botones del microwind enumeradas par su descripción 1) Open file: Este botón se utiliza para abrir cualquier archivo (*.MSK), con la ubicación y nombre

que se elija.

2) Save this file: Si presionas este botón el layout actual enun archivo (*.MSK), con la ubicación en disco y nombre que elija.

3) Draw box: Cuando se activa este botón, se puede dibujar sobre el espacio de trabajo de

Microwind, rectángulos del material seleccionado en la paleta de fondos (botón 19), del área que desees y con la escala de magnitud dada en lambda.

4) Delete some Layout: Este botón se utiliza para borrar toda clase de layers con solo hacer un clic sobre lo que se desee eliminar.

5) Copy elements: Si presionas este botón se puede copiar o clonar los layers de un área específica a otra parte del espacio de trabajo.

6) Stretch, move: Cuando se activa este botón, se puede cambiar las dimensiones de cualquier

layer, con solo hacer clic sobre cualquier parte del perímetro del layer a modificar, y mediante un arrastre de Mouse, asignar la nueva posición.

7) Zoom in: Este botón se utiliza para acercar la distancia de representación del layout en uso.

8) Zoom out: Si presionas este botón para alejar la distancia de representación del layout. Es el

complemento del Zoom in.

9) View all: Cuando se activa este botón se ajusta la distancia de representación al tamaño del

layout actual.

10) View electrical node: Presionando este botón y luego haciendo clic sobre cualquier punto del

workspace, se obtiene una visualización del nodo eléctrico (el nodo seleccionado se ve en colores, el resto del layout se muestra en color gris).

11) Run simulation: Si presionas este botón se despliega una ventana dinámica de simulación para el layout actual, donde se muestra comportamientos de tensión contra tiempo, tensión contra tensión, etc.

Figura 7. Ventana dinámica del botón Run simulation12) Measure distance: Cuando se activa este botón, se puede medir las distancias en el workspace.

13) 2D vertical cross-section: Al activar este botón y después hacer clic sobre un punto del workspace, se despliega una ventana mostrando una disposición vertical de la sección transversal que contiene al punto seleccionado.

14) Process steps in 3D: Si presionas este botón se despliega una ventana donde se muestran los

pasos del proceso de elaboración “real” en 3 dimensiones del circuito representado mediante el layout actual.

Figura 8. Se muestra un modelo 3D de una compuerta NAND hecho en Microwind16) Add text to layout: Este botón se utiliza para añadir un texto importante en alguna parte del layout.

17) Connect layers: Si presionas este botón y después presionas en un punto del workspace, se

creará en ese punto una unión metal contacto, que conecta todos los layers que se encuentran en ese punto.

18) Simulate MOS characteristics: Cuando se activa este botón se depliega una ventana donde se

muestran las características de corriente contra tensión y el comportamiento de las capacitancias internas conforme varian las tensiones de los posibles dispositivos MOS que se encuentren en el layout.

Figura 9. Características de un

MOS

Figura 10. Paleta de MicrowindDESARROLLO DEL TRABAJO:

A) TRANSISTOR N-MOS

1) Revisar el modelo teórico de spice shichman hodges (nivel 1), identifique los terminales del transistor n-mos (drain, source, gate, bulk) en su layout del transistor, muestre las ecuaciones del transistor en las zonas de corte, lineal, saturación. Interprete el layout realizado por Ud.

Modelo teórico de spice schichman hodges:

Construcción del transistor n-MOS usando el software Microwind

Tal y como se muestra en la figura 11, elegimos la difusión tipo N. Después hacemos clic en la pantalla y dibujamos un rectángulo. Tal y como se muestra en la figura 12.

Figura 11. Opción N+Diffusion seleccionada

Figura 12. Creamos la difusión tipo N

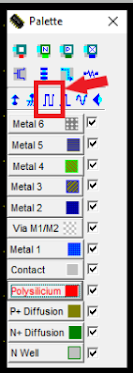

Ahora seleccionamos el polisilicio de color rojo (que será el terminal del gate).

Figura 13. Polisilicio

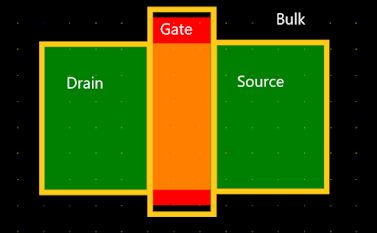

Identificamos ahora los distintos terminales del transistor n-MOS:

Figura 14. Identificación

de las terminales del transistor n-MOS

Ahora añadimos las fuentes respectivas. Añadimos una señal cuadrada en el terminal gate y drain, además en el terminal source colocamos un nodo visible:

Figura 15. Elegimos una señal

cuadrada

Introducimos los parámetros a los voltajes Vgate y Vdrain:

Figura 16. Definimos los parámetros para Vgate

Figura 17. Definimos los

parámetros para Vdrain

Figura 18. Elegimos un

nodo visible para Vsource

Figura 19. Declaramos el

nodo visible como Vsource

Figura 20. Layout del

transistor CMOS en Microwind

Ecuaciones del transistor

en las zonas de corte, lineal, saturación

Interpretación del layout

Como se puede observar, la construcción del layout de un transistor n-MOS es bastante sencillo. Su funcionamiento se puede explicar de la siguiente manera:

Figura 21. Transistor n-MOS

En un principio, cuando el MOSFET no está funcionando se creará una región de agotamiento entre los lados N y el sustrato P. Una región de agotamiento es cuando una zona se libera de electrones o agujeros libres.

Figura 22. Región de agotamiento en las uniones p-n en un transistor n-MOS

Ahora colocamos ahora una placa conductora y un aislante (terminal gate) al medio de las 2 zonas de difusión N, el sustrato tipo p del transistor se comportará como la otra placa y todo el sistema en conjunto parecerá un capacitor. Si le colocamos una fuente en una terminal se creará un campo eléctrico como se puede ver en la figura 23.

Figura 23. Campo eléctrico

creado por el voltaje Vgate

Ocurrirá

ahora que, debido al campo eléctrico, los portadores minoritarios del sustrato

(electrones) se juntaron con los huecos y crearon una nueva región de

agotamiento:

Figura 24. Nueva región de

agotamiento entre el drain y el source

Una

tensión positiva sobre el terminal Vgate da lugar a un canal continuo entre las

2 zonas de difusión N, que permite el flujo de corriente entre ellas. Para que

se forme una región de agotamiento entra las dos zonas n, debemos pasar un

voltaje de umbral VTO.

VG<VTO

(no existe canal -> el transistor no conduce)

VG<VTO (se forma canal -> el transistor conduce)

Si colocamos ahora otra fuente en los terminales drain y source, estos se podrán desplazar y de esa manera habremos obtenido un transistor n-MOSFET. El principio de funcionamiento en un CMOS es el mismo.

Figura 25. Flujo de

electrones desde el drain hacia el source

2) Muestre la pantalla de características estáticas, comportamiento dinámico, vista de corte, vista 3D, identifique los parámetros de dimensiones del layout.

Características estáticas:

Para ver las características estáticas del transistor n-MOS damos clic en el botón “Simulate MOS characteristics”:

Figura

26. Características estáticas del transistor n-MOS hecho en Microwind

Comportamiento dinámico:

Para ver el comportamiento dinámico seleccionamos “Simulate” y hacemos clic en “Start simulation”:

Figura

27. Comportamiento dinámico del transistor n-MOS hecho en Microwind

Vista de corte

Para la vista de corte seleccionamos “Process View” (primer icono) y hacemos un trazo en donde queremos ver la vista de corte:

Figura

28. Diseño 2-D del transistor n-MOS hecho en Microwind

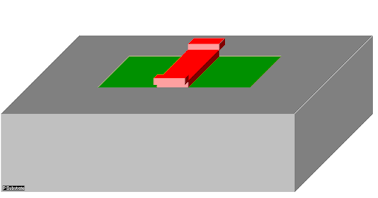

Vista 3D

Para la vista de corte seleccionamos “Process View” (segundo icono) y aparecerá la imagen del sustrato, si le damos clic en “Next Step” nos ira apareciendo las componentes del transistor.

Figura

29. Diseño 3-D del transistor n-MOS hecho en Microwind

3) Muestre la descripción *.cir (spice) del layout, describa el significado de cada línea de la descripción, identifique las dimensiones W y L de transistor, muestre en el layout la ubicación de las capacidades parasitas y su valor.

Para mostrar la descripción del layout (spice). Debemos ir a “File” y seleccionar “Make Spice File”. Nos aparecerá la siguiente figura:

Figura

30. Descripción (spice) del layout)

La descripción completa se muestra en la figura 31:

Figura 31. Descripción del

layout del transistor n-MOSFET

Descripción: Como podemos ver en la primera línea aparece la ruta de donde se encontrará este archivo. Podemos ver también las señales que hemos puesto para las entradas (Vdrain y Vgate), los tiempos de subida y bajada. Después podemos ver la lista de nodos: “Vsource” corresponde al nodo 2, “Vdrain” corresponde al nodo 3 y “Vgate” corresponde al nodo 4. Siguiendo con la descripción, en MOS device se puede ver que Microwind ha identificado el dispositivo como un transistor N, además nos da de manera exacta W (ancho de la difusión) y L (canal de conducción). En las siguientes líneas se muestran las capacidades parasitas en los nodos (Vsource, Vdrain y Vgate). Después aparecen los modelos del transistor (por defecto el Microwind utiliza el modelo 3), aquí aparecen los parámetros como Kp, VTO, theta, entre otros (para n-MOS y p-MOS).

De las características del transistor podemos observar que:

W=3.5 µm

L=1.38 µm

Figura 32. Layout del transistor con sus 3 capacitancias

parasitas

4) Proponga un procedimiento para hallar la resistencia de conducción del transistor (cuando opera en la zona de saturación). Considere el modelo de shichman hodges y asuma los parámetros de acuerdo a su layout.

Cuando el transistor opera en la zona de

saturación existe una corriente que está dada por:

Según los parámetros obtenidos del layout.

KP= 300(10-6)µA/V2

VTO=0.45 V

Cuando opera en la región de saturación consideramos: VGS=2.5v, y VDS=2.5v

B)

TRANSISTOR P-MOS

Igual que en la parte A, resuelva lo pedido en los puntos 1,2,3,4. En base al layout del transistor p-mos realizado por Ud.

1) Revisar el modelo teórico de spice shichman hodges (nivel 1), identifique los terminales del transistor p-mos (drain, source, gate, bulk) en su layout del transistor, muestre las ecuaciones del transistor en las zonas de corte, lineal, saturación. Interprete el layout realizado por Ud.

Modelo teórico de spice schichman hodges [4]:

Construcción del transistor p-MOS usando el software Microwind

Primero, para crear el transistor p-MOS debemos crear la capa “N Well”. Ademas de una fuente VDD.

Figura 33. Creación de la

capa N well

Elegimos de la paleta la difusión tipo P (P+ Diffusion). Después hacemos clic en la pantalla y dibujamos un rectángulo. Tal y como se muestra en la figura .

Figura 34. Creamos la

difusión tipo P

Ahora seleccionamos el polisilicio de color rojo (que será el terminal del gate).

Figura 35. Polisilicio

Identificamos ahora los distintos terminales del transistor p-MOS

Figura 36. Identificación

de las terminales del transistor p-MOS

Ahora añadimos las fuentes respectivas. Añadimos una señal cuadrada en el terminal gate y drain, además en el terminal source colocamos un nodo visible:

Figura 37. Elegimos una

señal cuadrada

Introducimos los parámetros a los voltajes Vgate y Vsource:

Figura 38. Colocamos los parámetros de Vgate

Figura 39. Colocamos los parámetros de Vsource

Figura 40. Elegimos un nodo visible para source

Figura 41. Nombramos al

nodo visible Vdrain

Figura 42. Layout del

transistor p-MOS en Microwind

Ecuaciones del transistor

en las zonas de corte, lineal, saturación

Interpretación del layout

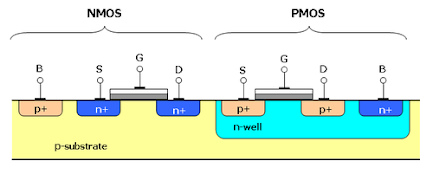

El tipo de funcionamiento en el transistor tipo p es el mismo que en el de tipo n, la única diferencia es que ahora el flujo será de huecos y no de electrones. Además, se polariza desde el terminal Vsource. A la hora de hacer el transistor se le debe poner un sustrato tipo n. En este imagen se puede comparar un transistor n-MOS con uno p-MOS:

Figura

43. Transistor n-MOS y p-MOS

2)

Muestre la pantalla de características estáticas, comportamiento

dinámico, vista de corte, vista 3D, identifique los parámetros de dimensiones

del layout.

Características estáticas

Para ver las características estáticas del transistor p-MOS damos clic en el botón “Simulate MOS characteristics”:

Figura

44. Características estáticas del transistor p-MOS hecho en Microwind

Comportamiento dinámico:

Para ver el comportamiento dinámico seleccionamos “Simulate” y hacemos clic en “Start simulation”:

Figura 45. Comportamiento dinámico del transistor p-MOS hecho en Microwind

Vista de corte

Para la vista de corte seleccionamos “Process View” (primer icono) y hacemos un trazo en donde queremos ver la vista de corte:

Figura

46. Diseño 2-D del transistor p-MOS hecho en Microwind

Vista 3D

Para la vista de corte seleccionamos “Process View” (segundo icono) y aparecerá la imagen del sustrato, si le damos clic en “Next Step” nos ira apareciendo las componentes del transistor.

Figura

47. Diseño 3-D del transistor p-MOS hecho en Microwind

3) Muestre la descripción *.cir (spice) del layout, describa el significado de cada línea de la descripción, identifique las dimensiones W y L de transistor, muestre en el layout la ubicación de las capacidades parasitas y su valor.

Para mostrar la descripción del layout (spice). Debemos ir a “File” y seleccionar “Make Spice File”. Nos aparecerá la siguiente figura:

Figura 48. Descripción (spice) del layout

La descripción completa se muestra en la figura 48.

Figura 49. Descripción del layout del transistor n-MOSFET

Descripción: Como podemos ver en la primera línea aparece la ruta de donde se encontrará este archivo. Podemos ver también las señales que hemos puesto para las entradas (Vdrain y Vgate), los tiempos de subida y bajada. Después podemos ver la lista de nodos: “Vsource” corresponde al nodo 3, “Vdrain” corresponde al nodo 4 y “Vgate” corresponde al nodo 5. Siguiendo con la descripción, en MOS device se puede ver que Microwind ha identificado el dispositivo como un transistor P, además nos da de manera exacta W (ancho de la difusión) y L (longitud del canal de conducción). En las siguientes líneas se muestran las capacidades parasitas en los nodos (Vsource, Vdrain y Vgate). Después aparecen los modelos del transistor (por defecto el Microwind utiliza el modelo 3), aquí aparecen los parámetros como Kp, VTO, theta, entre otros (para n-MOS y p-MOS).

De las características del transistor podemos observar que

W=2.75 µm

L= 1.5 µm

Figura 50. Layout del transistor con sus 3 capacitancias

parasitas

4) Proponga un procedimiento para hallar la resistencia de conducción del transistor (cuando opera en la zona de saturación). Considere el modelo de shichman hodges y asuma los parámetros de acuerdo a su layout.

Cuando el transistor opera en la zona de

saturación existe una corriente que está dada por:

Según los parámetros obtenidos del layout.

KP= 300(10-6)µA/V2

VTO=0.45 V

Cuando opera en la región de saturación consideramos: VGS=2.5 v, y VDS=2.5 v

CONCLUSIONES:

Ø Los transistores tipo n transmiten bien el 0 lógico, pero no el 1 lógico.

Ø Los transistores tipo p transmiten bien el 1 lógico, pero no el 0 lógico.

Ø Los transistores tipo p necesitan ser colocados sobre un sustrato tipo n cuando sean creadas.

Ø Los archivos .cir (spice) sirven para guardar la descripción del dispositivo creado.

Ø Existe una resistencia de conducción cuando el transistor está activado.

Ø Existen capacitancias parasitas entre las terminales del transistor y el sustrato.

Ø En el transistor tipo n se coloca el voltaje a la terminal drane y en el transistor tipo p se conecta el voltaje en la terminal de source.

BIBLIOGRAFIA:

·

[1]: Boylestad (pag. 401)

·

[2]: https://es.scribd.com/doc/251388359/Manual-Practico-de-Microwind-en-Espanol

(pag. 5)

·

[3]: https://es.scribd.com/doc/251388359/Manual-Practico-de-Microwind-en-Espanol

(pag. 7)

·

[4]: http://diec.unizar.es/~tpollan/libro/Apuntes/digT6.pdf

(pag. 10)