Autor: Alexis

LOGICA CMOS ESTATICA

Facultad de Ingeniería Electrónica y Eléctrica – UNMSM

1) Analizar y determinar la función lógica de salida

del circuito. Presentar completo el LAYOUT (manual con transistores de

dimensiones mínimas) y corroborar su función lógica mediante simulación.

Medir el ÁREA del layout y hallar la frecuencia MÁXIMA de operación. (Revisar el método para determinar la frecuencia de operación máxima de un circuito secuencial)

Funcionamiento del latch tipo

D: Vemos que cuando

la señal de clock se encuentra en “1” lógico, la señal de salida Q=D, pero si la

señal de clock se encuentra en “0” lógico, la señal de salida Q(t+1) =Q(t).

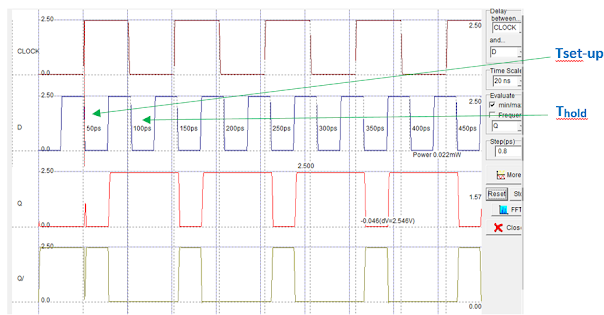

A continuación, se muestra la simulación de nuestro circuito secuencial latch tipo D. Vemos que mientras la señal de clock=”1” la salida “Q” es idéntica a la entrada “D”, mientras que si la señal clock=”0” la salida tomara el ultimo valor cuando la entrada clock fue “1”.

Figura 3: Simulación del layout del primer circuito

Latch D.

-El área ocupada del layout.

En la figura 4 observamos las dimensiones de nuestro layout,

que tiene un largo de 77 λ y un ancho de 53 λ, como λ=L/2=0.125µm realizamos

los siguientes cálculos:

Largo= 77 λ =77*(0.125µm) = 9.625 µm

Ancho= 53 λ =53*(0.125µm) = 6.625µm

El área ocupada seria=Largo*Ancho=9.625 µm*6.625µm =63.765625

(µm)2

Figura 4: Dimensiones del layout del primer circuito

Latch D.

-Hallar la frecuencia MÁXIMA

de operación.

Figura 5: Frecuencia máxima del layout del primer

circuito Latch D.

En la figura 6 mostramos la estructura para hallar la

frecuencia máxima a la que puede operar nuestro circuito secuencial. Primero

nuestro circuito lo divide en 2 partes, el primero es nuestra lógica

combinacional que se halla el tiempo de retraso entre la entrada y salida. El segundo

es nuestro circuito secuencial en el que se halla el Thold y Tset-up.

Figura 8: Tiempo de retardo Thold y Tset-up.

Como ya tenemos el retraso máximo de un circuito

combinacional, Thold y Tset-up podemos hallar la

frecuencia máxima del circuito secuencial.

Descripción del archivo Spice:

2) En base al layout de la parte 1, implementar un FF

tipo J-K disparado por flanco de subida. Hacer el layout manual de dimensiones

mínimas y corroborar su función lógica mediante simulación. Medir el ÁREA del

layout y hallar la frecuencia MÁXIMA de operación. (Revisar el método para

determinar la frecuencia de operación máxima de un circuito secuencial)

Figura 11: Layout del Flip flop tipo D.

En base a este flip flop tipo D, desarrollaremos un

flop flop tipo JK con ayuda de lógica combinacional, tal como se muestra a

continuación:

Desarrollamos la tabla de verdad del funcionamiento de

un Flip Flop tipo JK en base a uno de tipo D.

Figura 12: Tabla de verdad del Flip flop tipo D a JK.

Figura 13: Mapa de Karnaugh y circuito del Flip flop tipo D a JK.

Figura 14: Layout del Flip flop tipo JK.

-El área ocupada del layout.

En la figura 15 observamos las dimensiones de nuestro

layout, que tiene un largo de 164 λ y un ancho de 128 λ, como λ=L/2=0.125µm

realizamos los siguientes cálculos:

Largo= 164 λ =164*(0.125µm) = 20.5 µm

Ancho= 128 λ =128*(0.125µm) = 16 µm

El área ocupada seria=Largo*Ancho=20.5

µm* 16

µm =328 (µm)2

Figura 15: Dimensiones del layout del Flip Flop JK.

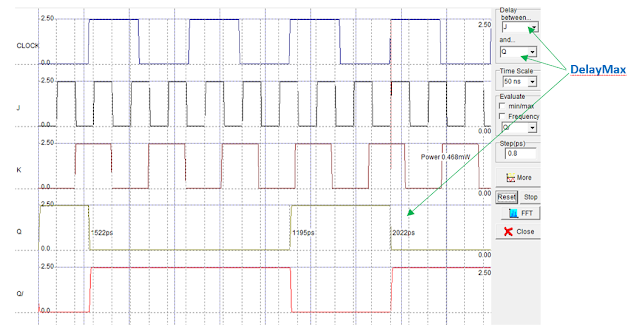

A continuación, se muestra la simulación de nuestro

circuito Flip Flop JK. Vemos que nuestro flip flop analiza las entradas J y K

cuando la señal de clock este en un flanco de subida. Teniendo en cuenta el

detalle de flanco se describirá todas a las posibles combinaciones. Cuando J= 0

y K=0 la salida permanece igual Q(t+1) =Q(t), cuando J= 0 y K=1 la salida pasa

a estado “0” lógico, cuando J= 1 y K=0 la salida pasa a estado “1” lógico y

finalmente cuando J= 1 y K=0 la salida invierte su estado

Figura 16: Simulación del layout del Flip Flop JK.

-Hallar la frecuencia MÁXIMA

de operación.

Primero definimos

el retraso máximo de nuestra lógica combinacional.

Figura 17: Retraso de la salida Q con respecto a la

entrada J.

Figura 18: Retraso de la salida Q con respecto a la

entrada K.

Haciendo un resumen de los retardos que tenemos de las diferentes entradas con respecto a la salida:

En la figura 7 vimos como hallar el Thold y Tset-up, que nos permiten hallar el retraso máximo en un circuito secuencial. En la figura 19 nuevamente mostramos la simulación, pero esta vez con las variables de clock con respecto a J y k que nos determinan estos parámetros de Thold y Tset-up.

Figura 19: Tiempo de retardo Thold y Tset-up.

Como ya tenemos el retraso máximo de un circuito

combinacional, Thold y Tset-up podemos hallar la

frecuencia máxima del circuito secuencial.

B) Para circuito

mostrado:

Figura 20: Circuito combinacional.

Analizar y determinar la función lógica de salida del circuito y dibuje el circuito esquemático de transistores.

Ahora dibujamos las conexiones de los transistores CMOS de otra manera.

En base a la red NMOS podemos construir nuestra función

booleana negada, que se muestra a continuación:

Negamos esta expresión para conseguir nuestra función

booleana.

Figura 23: Red PMOS y NMOS.

Tabla de verdad de nuestra función booleana.

|

A |

B |

C |

D |

FUNCIÓN |

|

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

0 |

0 |

1 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

0 |

|

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

Presentar completo el LAYOUT (manual con transistores de dimensiones mínimas) y corroborar su función lógica mediante simulación.

Figura 24: Layout de nuestro circuito combinacional.

A continuación, presentamos la simulación de nuestro layout.

Figura 25: Simulación de nuestro circuito

combinacional.

Medir el ÁREA del layout y

hallar la frecuencia MÁXIMA de operación.

Figura 26: Dimensiones del layout del circuito combinacional.

-El área ocupada del layout.

En la figura 26 observamos las dimensiones de nuestro

layout, que tiene un largo de 56 λ y un ancho de 44 λ, como λ=L/2=0.125µm

realizamos los siguientes cálculos:

Largo= 56 λ =56*(0.125µm) = 7 µm

Ancho= 44 λ =44*(0.125µm) = 5.5 µm

El área ocupada

seria=Largo*Ancho=7 µm* 5.5 µm = 38.5 (µm)2

-Hallar la frecuencia MÁXIMA

de operación.

Hallamos los

tiempos de retardos de la salida con respecto a cada entrada.

Figura 27: Retraso de la salida con respecto a la

entrada A.

Haciendo un resumen de los retardos que tenemos de las

diferentes entradas con respecto a la salida:

|

Delay Max |

Salida con A |

Salida con B |

Salida con C |

Salida con D |

|

Tiempo (ps) |

70 |

70 |

70 |

60 |

Teniendo en cuenta los valores anteriores, escogemos

el peor caso donde nuestra señal de retraso es mayor (70 ps) y en base a eso

hallamos la frecuencia máxima: