Autor: Alexis

DISEÑO GEOMÉTRICO DE TRANSISTORES MOS

1) Presentar el LAYOUT mínimo del inversor realizado por Ud. Considerar para el layout el esquema de la Fig. A y la Fig. B del diagrama de barras (STICK). Tratar de conseguir un layout de dimensiones mínimas. Mostrar y describir las vistas de corte 2D y 3D.

Figura 1: Layout del inversor en Microwind.

En la figura 1 se muestra el layout de un inversor

compuesto por un transistor Pmos que se encuentra al lado derecho juntamente

con su pozo nwell, este transistor es bueno transmitiendo los voltajes “1”,

razón por la cual es conectado a Vcc. En el lado izquierdo tenemos un

transistor cmos tipo n que es muy bueno transmitiendo los “0” razón por la cual

es conectada a tierra. Colocamos una señal de entrada cuadrada “Input” en el

“Polycilicium” que une los terminales “Gate” de ambos transistores, para

verificar la respuesta del layout, lo vemos a través de una señal de salida

llamada “Output”.

A continuación, se

muestra las vistas en 2d y 3d de nuestro layout.

En la figura 2 podemos apreciar la vista 2d de nuestro layout. Como se describió nuestro layout está compuesto por 2 transistores: 1 tipo p y 1 tipo n; En la parte inferior se puede observar el pozo nwell que permite polarizar correctamente para la formación del transistor cmos tipo p, de ahí se ve la difusión p+ y en el medio el bloque de “Polycilicium” que define el canal por donde circulara la corriente, con los parámetros W y L.

Figura 2: Vista en 2d del layout del inversor.

En la figura 3 podemos observar los 2 transistores:

tipo p (con su pozo nwell y p+ difusión) y tipo n (n+ difusion), en medio de

las difusiones vemos un bloque de color rojo que es el “Polycilicium” que es el

terminal “Gate” que nos permite controlar el paso o interrupción de la

corriente a través de la formación de un canal. Como las difusiones se

encuentra en diferentes capas, para hacer posible las conexiones se utiliza los

contactos que me permite conectar distintas capas.

Figura 3: Vista en 3d del layout del inversor.

2) Para el LAYOUT del inversor

(muestre el procedimiento empleado):

-Hallar la frecuencia MÁXIMA

de operación.

En la figura 3 podemos observar la simulación de nuestro layout, vemos que se comporta como un inversor, pero un detalle es el tiempo que se demora la señal de salida en cambiar de estado. Para cambia de “0” lógico a “1” lógico se demora 20 ps en cambio para pasar de “1” lógico a “0” lógico se demora 12ps, deducimos que nuestro inversos se demora más en los flancos de subida, para hallar la frecuencia máxima de operación hacemos so del mayor tiempo de cambio, que ocurre en un flanco de subida, de 20ps. Para hallar la frecuencia máxima se procede de la siguiente manera:

Como la señal de entrada posee una frecuencia de 1GHz,

no existe inconveniente.

Figura 3: Simulación del layout del inversor.

El área ocupada del layout.

En la figura 4 observamos las dimensiones de nuestro layout,

que tiene un largo de 55 λ y un ancho de 22 λ, como λ=L/2=0.125µm realizamos

los siguientes cálculos:

Largo= 55 λ =55*(0.125µm) =6.875 µm

Ancho= 22 λ =22*(0.125µm) = 2.75 µm

3) Para el LAYOUT del

inversor, extraer la descripción CIR (Spice) y la descripción CIF (Caltech

Intermediate Form) del inversor. En cada caso, establecer las reglas

principales de sintaxis y describir sus contenidos. Buscar en libro y/o

Internet la información necesaria.

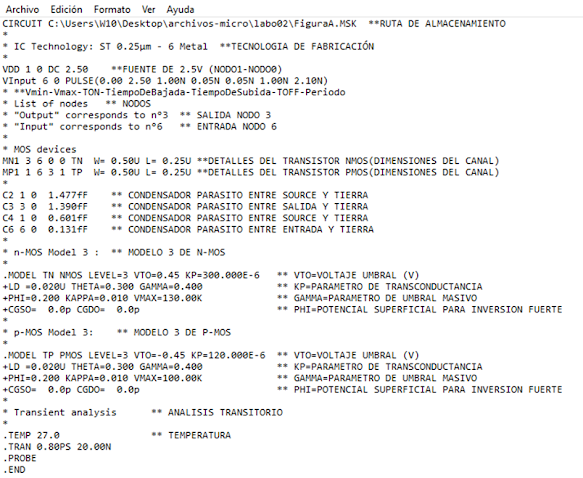

Lista de reglas para los ficheros. cir:

1)

La

primera línea será siempre el título y/o comentario del circuito.

2)

La

última línea será la sentencia. END (de final).

3)

Las

líneas que sean un comentario deben empezar con un asterisco (*).

4)

Las

líneas que sean una continuación de la sentencia de la línea anterior deben

empezar con un signo de suma (+).

5)

El

orden de las líneas que describen el circuito no importa, excepto para el

título, definiciones de subcircuitos, la sentencia .OPTIONS (de opciones).

6)

PSPICE

no diferencia letras mayúsculas de minúsculas, por lo que podemos utilizar

cualquiera de ellas.

7)

Para

separar los distintos parámetros de una sentencia, podemos usar espacios,

tabuladores o comas, que son equivalentes y no importa cuántas se usen.

Figura 5: Archivo .cir del layout del inversor.

Figura 6. Características del layout del inversor.

Para generar el archivo .cif se debe dar click en la

opción de la figura 6.

Figura 7: Archivo .cif del layout del inversor.

Después de realizar el paso anterior, se nos mostrara

un cuadro, tal como se ve en la figura 7, donde se hará click en el recuadro

“To CIF” para generar el archivo .cif

Figura 8: Generando Archivo .cif

-En base al archivo (*.cif) y

USANDO la vista del layout de su inversor, mediante líneas punteadas,

identifique los valores de las coordenadas (X,Y) que definen las capas de

polisilicion, difusiones, contactos y metal. Ver figura A, use una figura

similar solo para esta pregunta.

A continuación se muestra el contenido del archivo

.cif :

Figura 9: Enumerando las coordenadas del layout (Parte1).

Figura 10: Enumerando las coordenadas del layout (Parte 2).

4) Presentar el LAYOUT del

circuito mostrado en la Fig. C, revisar la teoría de su funcionamiento y

explique en detalle, página 165 del libro texto.

Figura C de la página 165 del libro.

Funcionamiento: Un trigger Schmitt cambia su estado de salida cuando

la tensión en su entrada sobrepasa un determinado nivel; la salida no vuelve a

cambiar cuando la entrada baja de ese voltaje, sino que el nivel de tensión

para el cambio es otro distinto, más bajo que el primero. A este efecto se

conoce como ciclo de histéresis. Ésta es la principal diferencia con un

comparador normal, que es un simple amplificador operacional sin

realimentación, y que su salida depende únicamente de la entrada mayor.

El trigger Schmitt usa la histéresis para prevenir el ruido que podría solaparse a la señal original y que causaría falsos cambios de estado si los niveles de referencia y entrada son parecidos.

Como caso particular

de pads de entrada se considera el llamado disparador de Schmitt (en inglés Schmitt

trigger). Es éste un buffer especial que se caracteriza por su función de

transferencia que presenta histéresis; es decir, la tensión de conmutación cuando

la entrada va desde ‘0’ a ‘1’ es diferente a la del caso en que la entrada va

desde ‘1’ a ‘0’ (Fig. 11).

Figura 11: Curva característica de entrada y salida

del disparador de Schmitt.

La utilidad de esta característica para un pad de entrada

se ilustra en la Fig. 12, en donde se muestra una forma de onda con reflexiones

y ruido (por ejemplo, causados por las interconexiones a nivel de PCB, como se

ha visto arriba en este mismo capítulo). Gracias a la diferencia en la tensión de

conmutación en un sentido y otro que presenta el disparador de Schmitt, la

salida del buffer presenta sólo una transición, eliminando el ruido siempre que

la amplitud de éste no supere ciertos valores: VDD-VTL para ruido de pulsos

invertidos (desde VDD), y VTH para ruido de pulso no invertido (desde 0 V).

El esquema eléctrico de un disparador de Schmitt se

muestra en la Fig. C. Un análisis de este circuito demuestra que su

comportamiento efectivamente presenta histéresis: si se considera que

inicialmente la entrada es 0 V y la salida VDD (el nodo de salida conectado a

VDD a través de los PMOS M4 y M5), se tendrá que el transistor M6 estará

cortado y el M3 en conducción, forzando por tanto una tensión igual a VDD-Vtn

en el surtidor de M2 (drenador de M1, estando ambos cortados ya que Vin es 0

V). A medida que la tensión de entrada Vin va subiendo, en el momento en que

llega a Vtn, M1 se pondrá en conducción de forma que habrá una corriente desde

VDD hasta GND a través de M1 y M3 que dará lugar a una tensión intermedia en

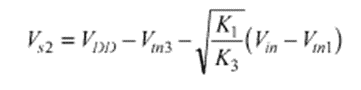

Vs2, dada por la expresión:

siendo Vtn1 y Vtn3 las tensiones umbral de M1 y M3 respectivamente, que serán diferentes debido al body effect. El transistor M2 seguirá cortado hasta que Vin sea mayor que Vs2+Vtn2 (y Vtn2 es igual a Vtn3 ya que M2 y M3 tienen el surtidor común). En ese momento M2 conducirá, con lo cual la tensión de salida empezará a bajar, disminuyendo la corriente a través de M3 y, por tanto, haciendo que Vs2 baje más rápidamente y forzando la transición. La tensión de entrada que causa esta transición es, muy aproximadamente, la tensión de conmutación del disparador VTH, y viene dado por la relación de transconductancias entre M1 y M3:

A continuación, en

la figura 13 presentamos nuestro layout de Trigger Schmitt:

)

Para circuito digital MOS mostrado en las Figura 15 Analizar y determinar la

función lógica de salida del circuito. Presentar completo el LAYOUT (manual y

de menor área) y corroborar su función lógica mediante simulación. Medir el

ÁREA del layout y hallar la frecuencia MÁXIMA de operación.

Figura 15: Circuito de función lógica.

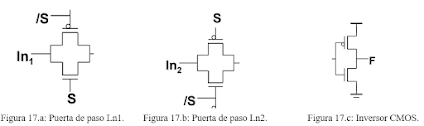

Como vemos en la figura 15 tenemos dos puertas de paso

para las señales de ln1 y ln2, además tenemos la señal de control S y su señal

invertida de S que controlan a las dos puertas, vemos que solo una puerta se

activa a la vez, en otras palabras, mientras S=1 se activa la puerta de paso de

ln1, para el caso S=0 se activa la puerta de paso para ln2, las salidas de

estas dos puertas de paso se conectan hacia un inversor que finalmente es la función

requerida. Haciendo un resumen completo, mientras que la señal de control S=1,

la salida será la señal inversa de ln1 y para el otro caso S=0, la salida será la

señal inversa de ln2.

En el circuito de nuestro layout vemos que está divido

en tres partes. La primera parte, tal como se muestra en la figura 17.a vemos

una puerta de paso con la variable de control S que controla la variable Ln1.

La segunda parte se muestra en la figura 17.b el cual es una puerta de paso con

la variable de control

Figura

18: Simulación de nuestro circuito.

-El área ocupada del layout.

En la figura 19 observamos las dimensiones de nuestro

layout, que tiene un largo de 74 λ y un ancho de 69 λ, como λ=L/2=0.125µm

realizamos los siguientes cálculos:

Largo= 74 λ =74*(0.125µm) = 9.25 µm

Ancho= 69 λ =69*(0.125µm) = 8.625 µm

Figura 19. Dimensiones del layout de la función lógica.

-Hallar la frecuencia MÁXIMA

de operación.

En la figura 20 podemos observar la simulación de

nuestro layout, vemos que se comporta como un inversor, pero un detalle es el

tiempo que se demora la señal de salida en cambiar de estado. Para cambia de

“0” lógico a “1” lógico se demora 120 ps y en otro paso de “0” lógico a “1”

lógico se demora 170ps, para hallar la frecuencia máxima de operación hacemos uso

del mayor tiempo de cambio, que ocurre en un flanco de subida, de 170ps. Para

hallar la frecuencia máxima se procede de la siguiente manera:

Como la señal de entrada posee una frecuencia de 250 MHz, 125 MHz y 62.5 MHz no existe inconveniente.