Autor: Mauro Benito Montoya Arenas (mauro2017pre@gmail.com)

Laboratorio N°7: “Diseño para testabilidad: modelo stuck-at 0 - stuck-at 1”

RESUMEN:

OBJETIVOS:

Ø Hacer las simulaciones de todas las fallas posibles stuck-at 0 y stuck-at 1 del circuito.

Ø Aprender el funcionamiento del modelo del stuck-at o y stuck-at 1 para detectar falas.

Ø Detallar

y describir la nueva salida del circuito debido a alguna falla provocada en una

línea

TEMA PROPUESTO:

Laboratorio N°7: “Diseño para testabilidad: modelo stuck-at 0 - stuck-at 1”

BASES TEORICAS:

DESARROLLO DEL TRABAJO:

I) De las

siguientes preguntas del Laboratorio N° 5: B, C

Elegir 01 (UNA) pregunta considerando las indicaciones dadas en cada pregunta. Adicionalmente se puede reducir el diseño a 3X3 bits. Se pide:

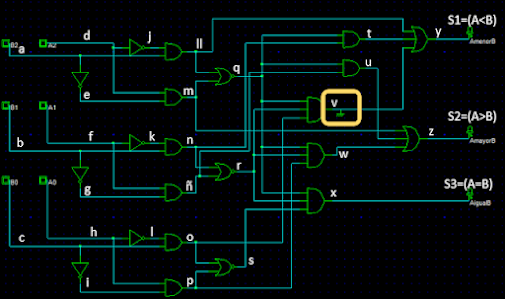

a) Determinar el número total de líneas del circuito que pueden tener los fallos S-AT-0 y S-AT-1.

Comparador

3x3 bits

Comparador 3x3 bits (complemento a 2)

|

Complemento a 2 |

Decimal |

|

011 |

3 |

|

010 |

2 |

|

001 |

1 |

|

000 |

0 |

|

111 |

-1 |

|

110 |

-2 |

|

101 |

-3 |

|

100 |

-4 |

b) Hallar el

conjunto mínimo de vectores de test para detectar todos los fallos S-AT-0 y

fallos S-AT-1.

Comparador 3x3 bits

|

Stuck-at

0 |

||||||||||||||||||||||||||||

|

A2A1A0B2B1B0 |

a0 |

b0 |

c0 |

d0 |

e0 |

f0 |

g0 |

h0 |

i0 |

j0 |

k0 |

l0 |

ll0 |

m0 |

n0 |

ñ0 |

o0 |

p0 |

q0 |

r0 |

s0 |

t0 |

u0 |

v0 |

w0 |

x0 |

y0 |

z0 |

|

000000 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

S3 |

S3 |

|

|

|

|

S3 |

|

|

|

011111 |

|

|

|

|

|

|

|

|

|

S1 |

|

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

S1 |

|

|

101111 |

|

|

|

|

|

|

|

|

|

|

S1 |

|

|

|

S1 |

|

|

|

|

|

|

S1 |

|

|

|

|

S1 |

|

|

110111 |

|

|

|

|

|

|

|

|

|

|

|

S1 |

|

|

|

|

S1 |

|

|

|

|

|

|

S1 |

|

|

S1 |

|

|

100000 |

|

|

|

|

S2 |

|

|

|

|

|

|

|

|

S2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

S2 |

|

010000 |

|

|

|

|

|

|

S2 |

|

|

|

|

|

|

|

|

S2 |

|

|

|

|

|

|

S2 |

|

|

|

|

S2 |

|

001000 |

|

|

|

|

|

|

|

|

S2 |

|

|

|

|

|

|

|

|

S2 |

|

|

|

|

|

|

S2 |

|

|

S2 |

|

111111 |

S2 |

S2 |

S2 |

S1 |

|

S1 |

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

|

|

Tabla 2. Tabla de fallos stuck

at 0

|

Stuck-at

1 |

||||||||||||||||||||||||||||

|

A2A1A0B2B1B0 |

a1 |

b1 |

c1 |

d1 |

e1 |

f1 |

g1 |

h1 |

i1 |

j1 |

k1 |

l1 |

ll1 |

m1 |

n1 |

ñ1 |

o1 |

p1 |

q1 |

r1 |

s1 |

t1 |

u1 |

v1 |

w1 |

x1 |

y1 |

z1 |

|

000000 |

S1 |

S1 |

S1 |

S2 |

|

S1 |

|

S2 |

|

|

|

|

S1 |

S2 |

S1 |

S2 |

S1 |

S2 |

|

|

|

S1 |

S2 |

S1 |

S2 |

|

S1 |

S2 |

|

011111 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

|

|

|

|

|

|

S3 |

|

S2 |

|

101111 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

|

|

|

|

|

S3 |

|

S2 |

|

110111 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

|

|

|

|

S3 |

|

S2 |

|

100000 |

|

|

|

|

|

|

|

|

|

|

|

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

S1 |

|

|

010000 |

|

|

|

|

|

|

|

|

|

|

|

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

S1 |

|

|

001000 |

|

|

|

|

|

|

|

|

|

|

|

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

S1 |

|

|

111111 |

|

|

|

|

S2 |

|

S1 |

|

S2 |

S1 |

S1 |

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S1 |

S2 |

Tabla 3. Tabla de fallos

stuck at 1

Comparador

3x3 bits (complemento a 2)

|

Stuck-at

0 |

||||||||||||||||||||||||||||

|

A2A1A0B2B1B0 |

a0 |

b0 |

c0 |

d0 |

e0 |

f0 |

g0 |

h0 |

i0 |

j0 |

k0 |

l0 |

ll0 |

m0 |

n0 |

ñ0 |

o0 |

p0 |

q0 |

r0 |

s0 |

t0 |

u0 |

v0 |

w0 |

x0 |

y0 |

z0 |

|

000000 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

S3 |

S3 |

|

|

|

|

S3 |

|

|

|

111011 |

|

|

|

|

|

|

|

|

|

S1 |

|

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

S1 |

|

|

101111 |

|

|

|

|

|

|

|

|

|

|

S1 |

|

|

|

S1 |

|

|

|

|

|

|

S1 |

|

|

|

|

S1 |

|

|

110111 |

|

|

|

|

|

|

|

|

|

|

|

S1 |

|

|

|

|

S1 |

|

|

|

|

|

|

S1 |

|

|

S1 |

|

|

000100 |

|

|

|

|

S2 |

|

|

|

|

|

|

|

|

S2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

S2 |

|

010000 |

|

|

|

|

|

|

S2 |

|

|

|

|

|

|

|

|

S2 |

|

|

|

|

|

|

S2 |

|

|

|

|

S2 |

|

001000 |

|

|

|

|

|

|

|

|

S2 |

|

|

|

|

|

|

|

|

S2 |

|

|

|

|

|

|

S2 |

|

|

S2 |

|

111111 |

S2 |

S2 |

S2 |

S1 |

|

S1 |

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

|

|

Tabla 4. Tabla de fallos stuck at

0

|

Stuck-at

1 |

||||||||||||||||||||||||||||

|

A2A1A0B2B1B0 |

a1 |

b1 |

c1 |

d1 |

e1 |

f1 |

g1 |

h1 |

i1 |

j1 |

k1 |

l1 |

ll1 |

m1 |

n1 |

ñ1 |

o1 |

p1 |

q1 |

r1 |

s1 |

t1 |

u1 |

v1 |

w1 |

x1 |

y1 |

z1 |

|

000000 |

S1 |

S1 |

S1 |

S2 |

|

S2 |

|

S2 |

|

|

|

|

S1 |

S2 |

S1 |

S2 |

S1 |

S2 |

|

|

|

S1 |

S2 |

S1 |

S2 |

|

S1 |

S2 |

|

111011 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

|

|

|

|

|

|

S3 |

|

S2 |

|

101111 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

|

|

|

|

|

S3 |

|

S2 |

|

110111 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

|

|

|

|

S3 |

|

S2 |

|

000100 |

|

|

|

|

|

|

|

|

|

|

|

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

S1 |

|

|

010000 |

|

|

|

|

|

|

|

|

|

|

|

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

S1 |

|

|

001000 |

|

|

|

|

|

|

|

|

|

|

|

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

S3 |

S1 |

|

|

111111 |

|

|

|

|

S2 |

|

S1 |

|

S2 |

S1 |

S1 |

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S1 |

S2 |

Tabla 5. Tabla de fallos

stuck at 1

c) Determinar si hay alguna línea del circuito que no es testable.

d) En el programa DSCH (desde el esquemático) simular el circuito con fallo, como mínimo para 02 de vectores de test encontrados en la parte b.

Comparación de 3x3 bits

Comparación de 3x3 bits (complemento a 2)

CONCLUSIONES:

Ø Todas las líneas pueden tener fallos stuck at 0 y stuck at 1. El total de fallos posibles en un circuito será de 2 por el número de líneas.

Ø Para analizar los fallos stuck at 0 y stuck at 1 debemos hallar vectores de test. Con estos vectores analizaremos la salida. Si el circuito no presenta fallas la salida será la esperada, pero si tiene fallas nos saldrá una salida que es distinta.

Ø Para circuitos grandes. La cobertura de la detección de fallos debe ser como mínimo del 95%.

Ø El

conjunto mínimo de vectores de test se refiere al conjunto de test suficientes

para detectar más del 95% de los fallos de un circuito.