Autor: Mauro Benito Montoya Arenas (mauro2017pre@gmail.com)

LABORATORIO N°6: “DISEÑO PARA TESTABILIDAD: MODELO STUCK OPEN – STUCK ON”

RESUMEN:

OBJETIVOS:

Ø Hacer las simulaciones de los stuck-on y stuck-open en dsch.

Ø Aprender sobre las modificaciones en la salida cuando en un transistor del circuito existe stuck on o stuck open.

Ø Detallar

las características de la salida cuando existe un stuck open o un stuck on.

TEMA PROPUESTO:

Laboratorio N°6: “Diseño para testabilidad: modelo

stuck open – stuck on”

BASES TEORICAS:

a)

Marco

Teórico:

Stuck

open:

a)

Marco

conceptual:

Software Microwind:DESARROLLO DEL TRABAJO:

1) De las siguientes preguntas del Laboratorio N° 4: 1, 2, 3, 5.

Resolver como mínimo 02 (DOS) preguntas usando con las indicaciones dadas. Para lógicas dinámicas considerar la señal φ = 1Ghz. Para cada circuito se pide:

a) Determinar el número de transistores del circuito que pueden tener los fallos S-OPEN y fallo S-ON.

Laboratorio Nº4: Pregunta 1

|

X1 |

X2 |

X3 |

X4 |

phi |

F |

|

|

0 |

0 |

0 |

0 |

0 |

1 |

Precarga |

|

0 |

0 |

0 |

0 |

1 |

1 |

Evaluación |

|

0 |

0 |

0 |

1 |

0 |

1 |

Precarga |

|

0 |

0 |

0 |

1 |

1 |

0 |

Evaluación |

|

0 |

0 |

1 |

0 |

0 |

1 |

Precarga |

|

0 |

0 |

1 |

0 |

1 |

0 |

Evaluación |

|

0 |

0 |

1 |

1 |

0 |

1 |

Precarga |

|

0 |

0 |

1 |

1 |

1 |

1 |

Evaluación |

|

0 |

1 |

0 |

0 |

0 |

1 |

Precarga |

|

0 |

1 |

0 |

0 |

1 |

0 |

Evaluación |

|

0 |

1 |

0 |

1 |

0 |

1 |

Precarga |

|

0 |

1 |

0 |

1 |

1 |

0 |

Evaluación |

|

0 |

1 |

1 |

0 |

0 |

1 |

Precarga |

|

0 |

1 |

1 |

0 |

1 |

0 |

Evaluación |

|

0 |

1 |

1 |

1 |

0 |

1 |

Precarga |

|

0 |

1 |

1 |

1 |

1 |

0 |

Evaluación |

|

1 |

0 |

0 |

0 |

0 |

1 |

Precarga |

|

1 |

0 |

0 |

0 |

1 |

0 |

Evaluación |

|

1 |

0 |

0 |

1 |

0 |

1 |

Precarga |

|

1 |

0 |

0 |

1 |

1 |

0 |

Evaluación |

|

1 |

0 |

1 |

0 |

0 |

1 |

Precarga |

|

1 |

0 |

1 |

0 |

1 |

0 |

Evaluación |

|

1 |

0 |

1 |

1 |

0 |

1 |

Precarga |

|

1 |

0 |

1 |

1 |

1 |

0 |

Evaluación |

|

1 |

1 |

0 |

0 |

0 |

1 |

Precarga |

|

1 |

1 |

0 |

0 |

1 |

1 |

Evaluación |

|

1 |

1 |

0 |

1 |

0 |

1 |

Precarga |

|

1 |

1 |

0 |

1 |

1 |

0 |

Evaluación |

|

1 |

1 |

1 |

0 |

0 |

1 |

Precarga |

|

1 |

1 |

1 |

0 |

1 |

0 |

Evaluación |

|

1 |

1 |

1 |

1 |

0 |

1 |

Precarga |

|

1 |

1 |

1 |

1 |

1 |

1 |

Evaluación |

|

|

|

|

|

|

X1 N-MOS |

/X1 N-MOS |

X2 N-MOS |

/X2 N-MOS |

X3 N-MOS |

/X3 N-MOS |

X4 N-MOS |

/X4 N-MOS |

|

X1 |

X2 |

X3 |

X4 |

F |

F-open |

F-open |

F-open |

F-open |

F-open |

F-open |

F-open |

F-open |

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

X1 N-MOS |

/X1 N-MOS |

X2 N-MOS |

/X2 N-MOS |

X3 N-MOS |

/X3 N-MOS |

X4 N-MOS |

/X4 N-MOS |

|

X1 |

X2 |

X3 |

X4 |

F |

F-on |

F-on |

F-on |

F-on |

F-on |

F-on |

F-on |

F-on |

|

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

Laboratorio Nº4: Pregunta 2

F(X1 , X2 , X3 , X4) = (X1

or X2 ) xor (X3 or X4 )

|

X1 |

X2 |

X3 |

X4 |

phi |

F |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

Precarga |

|

0 |

0 |

0 |

0 |

1 |

0 |

Evaluación |

|

0 |

0 |

0 |

1 |

0 |

0 |

Precarga |

|

0 |

0 |

0 |

1 |

1 |

1 |

Evaluación |

|

0 |

0 |

1 |

0 |

0 |

0 |

Precarga |

|

0 |

0 |

1 |

0 |

1 |

1 |

Evaluación |

|

0 |

0 |

1 |

1 |

0 |

0 |

Precarga |

|

0 |

0 |

1 |

1 |

1 |

1 |

Evaluación |

|

0 |

1 |

0 |

0 |

0 |

0 |

Precarga |

|

0 |

1 |

0 |

0 |

1 |

1 |

Evaluación |

|

0 |

1 |

0 |

1 |

0 |

0 |

Precarga |

|

0 |

1 |

0 |

1 |

1 |

0 |

Evaluación |

|

0 |

1 |

1 |

0 |

0 |

0 |

Precarga |

|

0 |

1 |

1 |

0 |

1 |

0 |

Evaluación |

|

0 |

1 |

1 |

1 |

0 |

0 |

Precarga |

|

0 |

1 |

1 |

1 |

1 |

0 |

Evaluación |

|

1 |

0 |

0 |

0 |

0 |

0 |

Precarga |

|

1 |

0 |

0 |

0 |

1 |

1 |

Evaluación |

|

1 |

0 |

0 |

1 |

0 |

0 |

Precarga |

|

1 |

0 |

0 |

1 |

1 |

0 |

Evaluación |

|

1 |

0 |

1 |

0 |

0 |

0 |

Precarga |

|

1 |

0 |

1 |

0 |

1 |

0 |

Evaluación |

|

1 |

0 |

1 |

1 |

0 |

0 |

Precarga |

|

1 |

0 |

1 |

1 |

1 |

0 |

Evaluación |

|

1 |

1 |

0 |

0 |

0 |

0 |

Precarga |

|

1 |

1 |

0 |

0 |

1 |

1 |

Evaluación |

|

1 |

1 |

0 |

1 |

0 |

0 |

Precarga |

|

1 |

1 |

0 |

1 |

1 |

0 |

Evaluación |

|

1 |

1 |

1 |

0 |

0 |

0 |

Precarga |

|

1 |

1 |

1 |

0 |

1 |

0 |

Evaluación |

|

1 |

1 |

1 |

1 |

0 |

0 |

Precarga |

|

1 |

1 |

1 |

1 |

1 |

0 |

Evaluación |

|

|

|

|

|

|

X1 N-MOS |

/X1 N-MOS |

X2 N-MOS |

/X2 N-MOS |

X3 N-MOS |

/X3 N-MOS |

X4 N-MOS |

/X4 N-MOS |

|

X1 |

X2 |

X3 |

X4 |

F |

F-open |

F-open |

F-open |

F-open |

F-open |

F-open |

F-open |

F-open |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

|

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

|

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

|

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

X1 N-MOS |

/X1 N-MOS |

X2 N-MOS |

/X2 N-MOS |

X3 N-MOS |

/X3 N-MOS |

X4 N-MOS |

/X4 N-MOS |

|

X1 |

X2 |

X3 |

X4 |

F |

F-on |

F-on |

F-on |

F-on |

F-on |

F-on |

F-on |

F-on |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

|

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Laboratorio Nº4: Pregunta 3

G (X1 , X2 , X3 , X4) = F and X4 F( X1 , X2 , X3 ) = X1 xor X2 xor X3

|

X1 |

X2 |

X3 |

F |

X4 |

G |

phi |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Precarga |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Evaluación |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

Precarga |

|

0 |

0 |

0 |

0 |

1 |

0 |

1 |

Evaluación |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

Precarga |

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

Evaluación |

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

Precarga |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

Evaluación |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

Precarga |

|

0 |

1 |

0 |

1 |

0 |

0 |

1 |

Evaluación |

|

0 |

1 |

0 |

0 |

1 |

0 |

0 |

Precarga |

|

0 |

1 |

0 |

1 |

1 |

1 |

1 |

Evaluación |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

Precarga |

|

0 |

1 |

1 |

0 |

0 |

0 |

1 |

Evaluación |

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

Precarga |

|

0 |

1 |

1 |

0 |

1 |

0 |

1 |

Evaluación |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

Precarga |

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

Evaluación |

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

Precarga |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

Evaluación |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

Precarga |

|

1 |

0 |

1 |

0 |

0 |

0 |

1 |

Evaluación |

|

1 |

0 |

1 |

0 |

1 |

0 |

0 |

Precarga |

|

1 |

0 |

1 |

0 |

1 |

0 |

1 |

Evaluación |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

Precarga |

|

1 |

1 |

0 |

0 |

0 |

0 |

1 |

Evaluación |

|

1 |

1 |

0 |

0 |

1 |

0 |

0 |

Precarga |

|

1 |

1 |

0 |

0 |

1 |

0 |

1 |

Evaluación |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

Precarga |

|

1 |

1 |

1 |

1 |

0 |

0 |

1 |

Evaluación |

|

1 |

1 |

1 |

0 |

1 |

0 |

0 |

Precarga |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Evaluación |

|

|

|

|

|

|

X1 N-MOS |

/X1 N-MOS |

X2-1 N-MOS |

X2-2 N-MOS |

/X2-1

N-MOS |

/X2-1

N-MOS |

X3 N-MOS |

/X3 N-MOS |

X4 N-MOS |

|

X1 |

X2 |

X3 |

X4 |

G |

G-open |

G-open |

G-open |

G-open |

G-open |

G-open |

G-open |

G-open |

G-open |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

|

|

|

|

|

|

X1 N-MOS |

/X1 N-MOS |

X2 N-MOS |

X2 N-MOS |

/X2 N-MOS |

/X2 N-MOS |

X3 N-MOS |

/X3 N-MOS |

X4 N-MOS |

|

X1 |

X2 |

X3 |

X4 |

G |

G-on |

G-on |

G-on |

G-on |

G-on |

G-on |

G-on |

G-on |

G-on |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

b) Elegir y hallar el vector/vectores de test para detectar 02 fallos S-OPEN y 02 fallos S-ON

Laboratorio Nº4: Pregunta 1

S-OPEN en el transistor tipo n de entrada X1

Vectores de inicialización:

Precarga: <X1,X2,X3,X4,phi>=<X,X,X,X,0>

-->F=1 (todas las combinaciones: 16)

S-OPEN en el transistor tipo n de

entrada /X3

Laboratorio Nº4: Pregunta 2

S-OPEN en el transistor tipo n de

entrada /X1

S-OPEN en el transistor tipo n de

entrada X4

S-ON en el transistor tipo n de

entrada X2

S-ON en el transistor tipo n de

entrada X3

Laboratorio Nº4: Pregunta 3

S-OPEN en el transistor tipo n de entrada X2(1)

Para la salida F:

S-OPEN en el transistor tipo n de

entrada /X3

S-ON en el transistor tipo n de

entrada X1

Para la salida F:

S-ON en el transistor tipo n de

entrada /X1

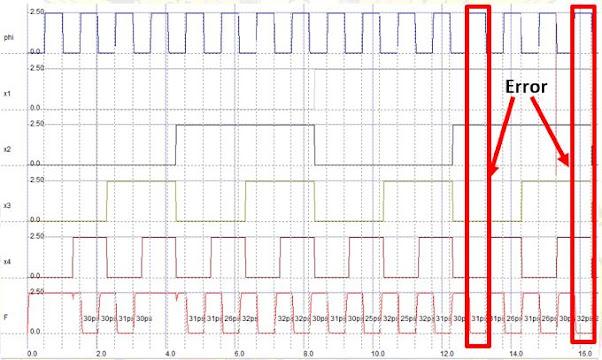

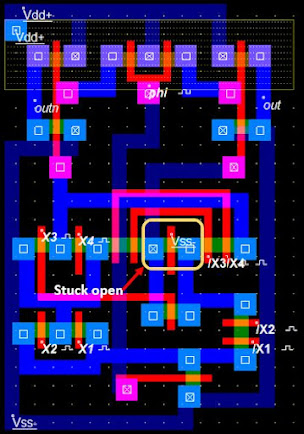

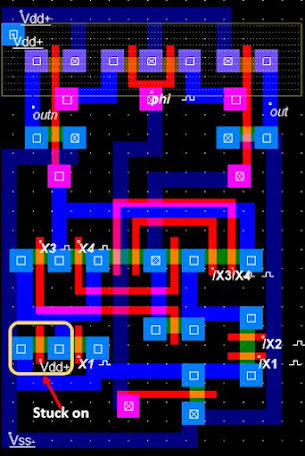

c) De forma conveniente, en el programa DSCH (esquemático) y Microwind (layout) inyectar manualmente y simular los fallos anteriores. Considerar los transistores de dimensiones mínimas (L=0.25 micras).

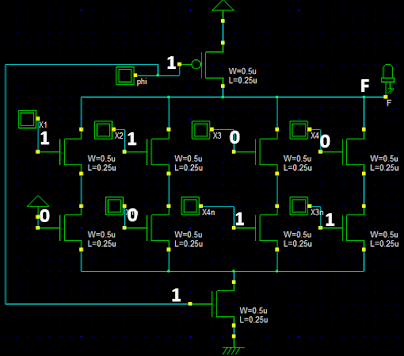

Laboratorio Nº4: Pregunta 1

S-OPEN en el transistor tipo n de entrada X1

S-OPEN en el transistor tipo n de

entrada /X3

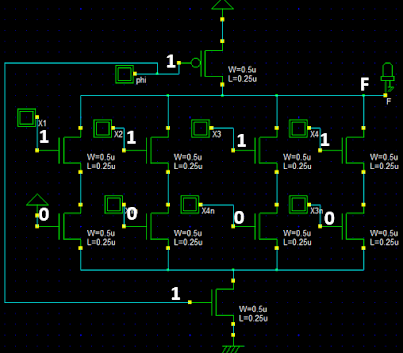

S-ON en el transistor tipo n de

entrada /X2

S-ON en el transistor tipo n de entrada

X4

Laboratorio Nº4: Pregunta 2

S-OPEN en el transistor tipo n de

entrada /X1

S-OPEN en el transistor tipo n de

entrada X4

S-ON en el transistor tipo n de

entrada X2

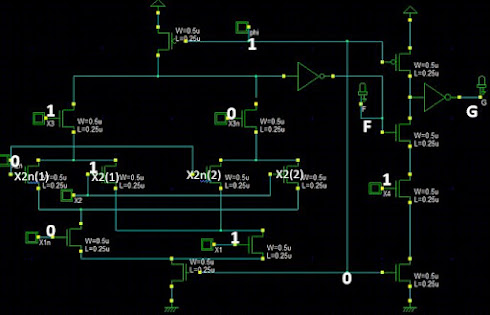

Laboratorio Nº4: Pregunta 3

S-OPEN en el transistor tipo n de

entrada X2(1)

S-OPEN en el transistor tipo n de

entrada /X3

d) Verificar

si hay algún transistor del circuito que no sea testable.

-

Laboratorio Nº4: Pregunta 3

G (X1 , X2 , X3 , X4) = F

and X4 F( X1 , X2 , X3 ) = X1 xor X2 xor X3

|

X1 |

X2 |

X3 |

X4 |

phi |

F |

F (stuck-open en X4) |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Precarga |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

Evaluación |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

Precarga |

|

0 |

0 |

0 |

1 |

1 |

1 |

0 (error) |

Evaluación |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

Precarga |

|

0 |

0 |

1 |

0 |

1 |

1 |

0 (error) |

Evaluación |

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

Precarga |

|

0 |

0 |

1 |

1 |

1 |

1 |

0 (error) |

Evaluación |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

Precarga |

|

0 |

1 |

0 |

0 |

1 |

1 |

0 (error) |

Evaluación |

|

0 |

1 |

0 |

1 |

0 |

0 |

0 |

Precarga |

|

0 |

1 |

0 |

1 |

1 |

0 |

0 |

Evaluación |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

Precarga |

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

Evaluación |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

Precarga |

|

0 |

1 |

1 |

1 |

1 |

0 |

0 |

Evaluación |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

Precarga |

|

1 |

0 |

0 |

0 |

1 |

1 |

0 (error) |

Evaluación |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

Precarga |

|

1 |

0 |

0 |

1 |

1 |

0 |

0 |

Evaluación |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

Precarga |

|

1 |

0 |

1 |

0 |

1 |

0 |

0 |

Evaluación |

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

Precarga |

|

1 |

0 |

1 |

1 |

1 |

0 |

0 |

Evaluación |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

Precarga |

|

1 |

1 |

0 |

0 |

1 |

1 |

0 (error) |

Evaluación |

|

1 |

1 |

0 |

1 |

0 |

0 |

0 |

Precarga |

|

1 |

1 |

0 |

1 |

1 |

0 |

0 |

Evaluación |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

Precarga |

|

1 |

1 |

1 |

0 |

1 |

0 |

0 |

Evaluación |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

Precarga |

|

1 |

1 |

1 |

1 |

1 |

0 |

0 |

Evaluación |

CONCLUSIONES

Ø El stuck on y stuck open se analizan de forma similar para los circuitos dinámicos.

Ø Un circuito no testable se refiere a un circuito cuyas salidas son todas “0” o “1” (no existen vectores de inicialización).

Ø Podemos comprobar la nueva salida cuando existe un stuck open o stuck on simulando el error (en caso de un stuck open en un transistor n podemos ponerlo a tierra y en caso de un stuck on en un transistor n podemos ponerlo a fuente).

Ø Los

vectores de inicialización en un circuito dinámico siempre serán las etapas en

la que el transistor está en precarga.